1 ‑ Nature du

travail

Le problčme se

résume ŕ réaliser sur un support, généralement du silicium mais pas

seulement des zones parfaitement déterminées dans lesquelles on

pourra faire pousser du silicium (épitaxie), introduire du dopant

(diffusion, implantation), faire croître de l'oxyde, créer une

connexion etc

2 - Création

des zones

De façon générale, il s'agit de

protéger la plaquette de silicium qui va recevoir les composants,

diodes, transistors, circuits intégrés, puis de dégager des espaces qui

vont faire l'objet d'un travail, le travail exécuté, il faut éliminer la

protection, recouvrir d'une nouvelle protection, dégager de

nouvelles zones etc

Le masquage

Le masquage proprement dit consiste ŕ protéger les zones qui ne

doivent pas recevoir de dopant ou d'oxyde ou autre ŕ l'aide d'un matériau "étanche", qui

pourra ętre une résine photosensible ou de l'oxyde de silicium

(Si02).

La

photo-lithogravure:

C'est Jean Hoerni (

photo de droite) qui créa le premier transistor par

photo-lithogravure le 2n1613 en 1958 chez Fairchild

semiconductor. Son procédé allait révolutionner la

technique de fabrication des semi-conducteurs

Le processus passe d'abord par la réalisation des masques qui seront

ensuite utilisés comme les typons des circuits imprimés pour

l'insolation de la résine photosensible déposée sur le silicium. Le

révélateur éliminera ensuite la résine qui a été ou qui n'a pas été

insolée (résine positive ou négative). Le silicium aprčs passage au

révélateur se retrouve ŕ nu ŕ certains endroits permettant ainsi la

pénétration du dopant ou toute autre opération.

C'est le procédé de photo lithographie

Les

problčmes de la photo lithographie:

Les

dimensions des motifs les plus petits descendent maintenant en

dessous du micron (1μm=10‑6m

et męme de quelques dizaines de nanomčtres ) ce qui entraîne des

problčmes considérables:

|

|

la diffraction de la lumičre

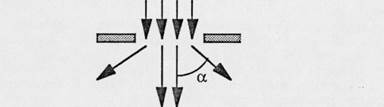

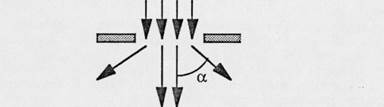

On sait qu'un

faisceau de lumičre parallčle, en passant par un orifice, diverge (

diffraction de Fraunhofer), cette divergence, tangente de l'angle α,

est donnée par la formule:

|

Hoerni est un ingénieur

suisse né en 1924 il s'installe aux Etats Unis en 1952

oů il fait la connaissance de William Schockley. Il

travaille dans le laboratoire de celui-ci et le quitte

avec 7 autres collčgues pour créer Fairchild en 1957.En

1958 Noyce invente le Circuit intégré sur silicium et de

son coté Hoerni met au point la technique de

photo-lithogravure

|

diffraction

de la lumičre traversant un orifice

Un faisceau

lumineux dont la longueur d'onde λ = 1μm (proche infrarouge) passant

dans un orifice de diamčtre d = 1μm aura un angle α de 50° environ . Il

découle de ce phénomčne que lorsque la lumičre passe ŕ travers les

motifs d'un masque, un manque de netteté des ombres projetées. Pour

éviter ou tout au moins réduire ce phénomčne on aura intéręt ŕ

utiliser un rayonnement de faible longueur d'onde qui peut atteindre

λ=0,193 μm (raie du fluorure d'argon)

La

réalisation des masques

La réalisation des masques, leur stabilité dimensionnelle

et de leur positionnement lors de masquages successifs posent des

problčmes considérables. La précision du positionnement

ŕ l'origine n'était pas parfaite, aussi il fallait en tenir compte sur le dimensionnement des

motifs.

Au début, le masque était en verre. Réalisé ŕ

l'échelle 1 il était plaqué sur le wafer ( tranche de silicium )

enduit de résine photosensible. Exposé ŕ la lumičre, tous les futurs

circuits intégrés étaient insolés en męme temps.

Placer le masque sur le silicium l'endommageait rapidement, les

défauts apparus sur le masque se répétaient ŕ chaque insolation. La

durée de vie d'un masque était de 25 ŕ 50 insolations.

Ajoutons que pour réaliser un circuit intégré, chaque couche

nécessite un masquage. Les premiers circuits nécessitaient 8

masques. Les techniques modernes, qui associent plusieurs millions

voir centaines de millions de transistors dans un circuit,

nécessitent 25 masques , ce sont 500 opérations qui peuvent s'échelonner

sur un mois.

Chaque couche va entraîner une série d'opérations:

nettoyage, séchage, dépôt de résine, cuisson de la résine, insolation,

développement, nettoyage, attaque chimique, dépôt ou diffusion ou

oxydation ou ..., Chaque masquage peut nécessiter 20 opérations.

Actuellement, les masques sont réalisés ŕ l'échelle 5 une optique

ramčne le faisceau ŕ la dimension normale mais les circuits sont

réalisés un par un. Le wafer est fixé sur une table X-Y de grande

précision, ŕ positionnement par interférométrie laser qui déplace le

silicium aprčs chaque insolation.

Les masques peuvent ętre réalisés eux męmes ŕ l'aide d'un faisceau

d'électron de 1μm de diamčtre

(la longueur d'onde associée ŕ une énergie de

10 KeV est de 1Ǻ) les débuts

de cette technique ont été effectués en détournant l'emploi d'un microscope

électronique. La pičce ŕ irradier est fixée sur une table XY de

grande précision positionnée par interférométrie laser. Le faisceau

d'électrons est focalisé ŕ l'aide de lentilles électroniques mais

n'insole la cible que point par point ce qui est lent

Les sources d'insolation

En pratique, les dimensions minimales des motifs sont voisines de la

longueur d'onde du rayonnement utilisé.

La technologie 0,25 μm (taille du motif minimum) est obtenu avec une

source UV de longueur d'onde λ=0,248 μm utilisant du fluorure de

krypton.

Des lasers ŕ fluorure de krypton

peuvent produire un rayonnement de λ=0,193 μm . Il permet

d'obtenir des motifs de 0,13 μm et męme 0,09 μm

L'utilisation des UV n'est pas sans poser de problčme, les

verres et męme le quartz deviennent absorbants, il faut utiliser une

optique en Fluorite CaF2 et męme des miroirs métalliques de grande

précision.

Une technique également en cours d'étude consiste ŕ

produire un rayonnement de λ 13,5 nm en éclairant avec un laser une

bille d'étain qui émet alors ce rayonnement mais actuellement la

puissance de l'émission est limité ŕ 10 Watts alors que 100 ŕ 250 W

seraient nécessaires. Les choses se compliquent du fait que le

rayonnement de cette longueur d'onde n'est pas transmis par l'air,

il est donc nécessaire de travailler sous vide. Il devrait ętre

possible de réaliser des lignes espacées de 10nm

3 - Le dopage du silicium

Pour obtenir du Silicium N on introduit un dopant de valence 5 qui

pourra ętre de l'Antimoine, du Phosphore, de l'arsenic ou du

Lithium.

Le Silicium P est obtenu par dopage avec un matériau de valence 3

tel que Gallium, Indium, Bore ou Aluminium

Plusieurs techniques sont possibles, le monocristal peut ętre dopé

au moment de son étirage, il s'agit évidemment d'un dopage uniforme

de tout l'ensemble du monocristal. Ceci est obtenu en introduisant

dans le creuset un mélange de Silicium et de dopant. Cela suppose au

départ pour ces deux matériaux, des températures de fusion voisines

et une solubilité du dopant dans le silicium.

3 - 1 ‑ L'épitaxie

L'épitaxie consiste ŕ faire croître sur du Silicium pur ou déjŕ

dopé, du silicium dopé différemment. Les plaquettes de Silicium sont

disposées dans un four ŕ atmosphčre contrôlée et portées ŕ une

température de 1200°C environ. Un mélange gazeux circule au contact

avec les plaquettes. Ce gaz est un composé chimique du corps ŕ faire

croître contenant notamment, du Silicium, du dopant et de

l'hydrogčne. Une réaction chimique se produit et une couche croît

sur le silicium véritable progression du monocristal de base.

L'épaisseur des couches obtenues dépend du temps de chauffage, elles

peuvent atteindre 25 μm.

3 ‑

2 ‑ Diffusion

La

diffusion est associée ŕ la technique de masquage, en effet, pour

permettre une diffusion locale du dopant dans le Silicium, il est

nécessaire de protéger les autres zones.

La plaquette de Silicium est chauffée ŕ 1000°C environ en présence

d'un gaz contenant le dopant. Ce dernier migre dans le Silicium aux

endroits non protégés. Évidemment, la concentration obtenue forte en

surface, décroît avec la profondeur, les zones masquées ne sont pas

entičrement protégées car la migration n'est pas uniquement

perpendiculaire ŕ la surface.

Diffusion du dopant

dans le silicium

Le profil de la

diffusion dépend essentiellement des matériaux en présence et suit

une loi non modifiable.

Profils de

diffusion de dopants dans le silicium

Le dopage par

diffusion présente donc les inconvénients suivants:

- La répartition du dopant subit une loi

non modifiable

- Le dopant diffuse

sous les protections

Toutes les impuretés contenues dans le gaz diffusent dans le

Silicium et pas seulement le dopant

3 - 3 L'implantation ionique

Le

procédé d'implantation ionique consiste ŕ projeter sur le silicium

des ions de dopant. Le dopant est d' abord ionisé puis accéléré par

un champ électrique avec la plaquette de silicium comme cible

(énergie de 30 ŕ 200 keV ) Le faisceau d'ions est modulé et dirigé ŕ

l'aide de lentilles électroniques et de plaques de déflexion. Le

faisceau peut ętre dirigé avec précision, le masquage devient alors

inutile en outre le contrôle de l'énergie des ions permet une

certaine maîtrise du profil du dopage.

Dans le cas de l'implantation ionique, le masquage n'est pas

nécessaire mais en fait , les commandes qui pilotent les plaques de

déflexion contiennent toutes les informations d'un masque. On parle

communément de masquage électronique. Les informations sont

contenues dans la mémoire de l'ordinateur qui commande la déflexion

du faisceau d'ions.

Cependant, cette technique présente un inconvénient, le dopant en

pénétrant dans le silicium peut créer des dislocations (

irrégularités dans l'organisation cristalline ), un recuit

(chauffage uniforme de la plaquette aprčs implantation) peut palier

cet inconvénient mais il modifie le profil des dopages

En 2007 état de la technique était gravure 90

et 65nm, longueur de canal 45 ou 35 nm, épaisseur de l'oxyde moins

de 4 nm, 7 ŕ 10 niveaux d'interconnexion isolé par 1μm d'oxyde

, 25 masques, 500 opérations s'étalant sur 1 mois

En 2012

Intel sort le 95xx Itanium Poulson

4 ou 8 cśurs. Il travaille ŕ

des fréquences qui vont de 1,7 ŕ 2,5 GHz et permet 6400 Méga Transferts

par seconde, consomme 130 ŕ 170 W réunit

3,1 109

transistors. Gravure

0,032 μm surface de silicium 544 mm2

En 2014 l'industrie des circuits intégrés ŕ produit 250 1018

transistors (250 milliards de milliard de transistors) , 8 milliards

de transistors par seconde

Aux derničres nouvelles (2015) IBM et Intel sont en lutte pour

produire des circuits en gravure 14, 10 et 7 nm

Une grande

partie de cette fiche est réalisée ŕ partir de "Histoire de la

microélectronique" de Philippe Matherat qu'on peut trouver sur le

site;

https://cel.archives-ouvertes.fr/cel-00157199/document

Les étapes jusqu'aux CCD