Circuits logiques DTL et TTL

|

|

|

|

Orville Baker Physicien américain Concepteur des circuits DTL |

James Buie Physicien américain 1920 - 1988 Concepteur des circuits TTL 1962 |

Thomas Longo Physicien américain Concepteur des circuits TTL 1962 |

|

Orville Baker

concepteur des circuits DTL . Une premičre famille de circuits utilisant des transistors bipolaires avait été conçue, la famille RTL (voir la fiche sur les circuits intégrés en général) n'était pas satisfaisante , deux tensions d'alimentation, immunité au bruit variable en fonction du nombre d'entrées connectées etc. Orville aprčs ses études de physique en 1956 est recruté par IBM, lŕ il rencontre Noyce et Tom Bay (directeur du marketing de Fairchild) . En 1959 il est recruté par Fairchild et en 1961 il rejoint les fondateurs de Signetics qui a la banque Lehman Brothers comme financier. Il va s'évertuer ŕ intégrer un circuit qu'il a déjŕ étudié ŕ l'aide de composants discrets chez IBM composé essentiellement de diodes et de transistors. En 1962 Signetics sort le premier circuit DTL . Ce circuit aura l'effet d'une bombe dans le monde de l'électronique. Plusieurs socičtés vont fabriquer les circuits DTL et notamment Fairchild qui va concevoir grâce ŕ sa technicité dans le domaine de l'intégration des circuits utilisant moins de silicium. Moins de matičre, plus de circuit sur la plaquette de silicium (Waffer) réalisés simultanément donc moindre coűt. Baker sera membre du conseil d'administration de Signetics de 1965 ŕ 1970 puis il passera chez National Semiconductor (NS) pour travailler sur les microcontrôleurs |

|

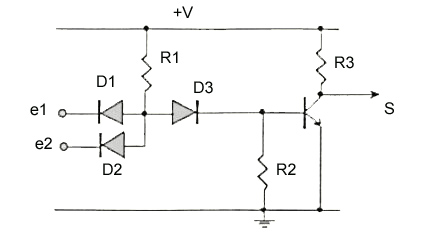

Exemple de porte DTL Nand ŕ 2 entrées |

|

La porte DTL fut le premier

pas vers la production de masse des circuits intégrés logiques. Le

schéma est simple et son emploi également. Une version ŕ haute

immunité au bruit pour les milieux industriels sortira plus tard oů

la diode D3 sur le schéma ci dessus est remplacé par une diode zener.

La HL DTL (high level DTL) qui est alimentée en 12 volts..

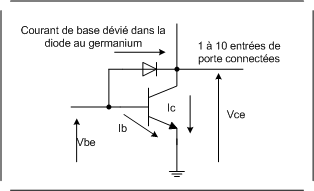

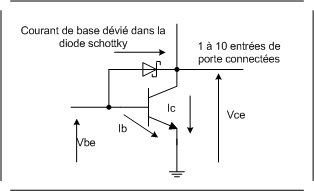

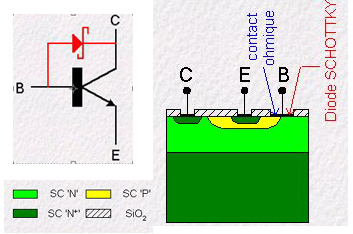

Lorsqu'un transistor est

saturé il est lent ŕ se bloquer, il faut écouler toutes les

charges contenues dans les jonctions.

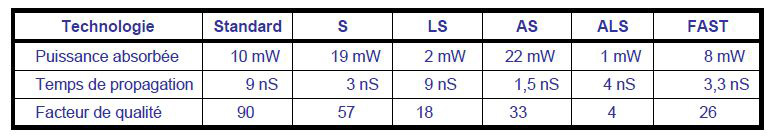

Le facteur de qualité , fdq, est le produit de la consommation d'une porte par son temps de propagation, plus il est petit plus la porte est performante ( en principe) Les étapes jusqu'aux CCD

|

||||||

|

||||||

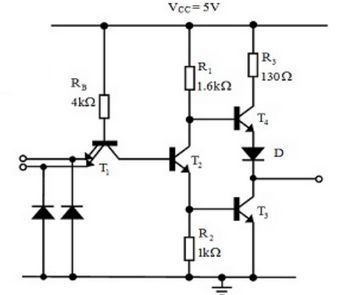

Commercialisée

en 1963 la logique TTL va devenir la famille la plus

courante pendant 20 ans.

Commercialisée

en 1963 la logique TTL va devenir la famille la plus

courante pendant 20 ans.

Si l'utilisation

nécessite une commutation rapide, on devra s'évertuer de ne

pas saturer les transistors.

Si l'utilisation

nécessite une commutation rapide, on devra s'évertuer de ne

pas saturer les transistors.