|

Hannon Yourke Jan

Narud |

|

|

||||

|

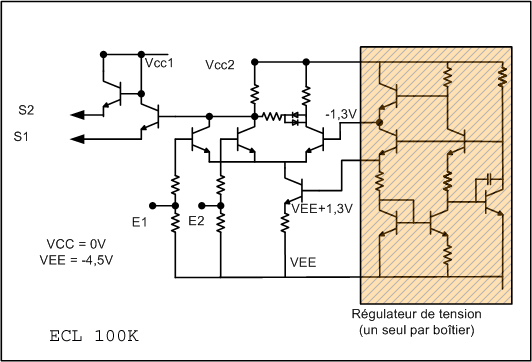

1956 - Hannon Yourke: diplômé du MIT, en 1954 il travaille pour IBM avec comme objectif d'accélérer la vitesse de commutation des portes logiques. Le point fondamental était de ne pas saturer les transistors , en effet , un transistor saturé est long à sortir de la saturation, donc à se bloquer. Pour cela, il est nécessaire d'évacuer toutes les charges stockées dans les jonctions. Yourke part alors sur le principe d'un amplificateur différentiel mais les transistors de l'époque, transistors à point de contact, n'avaient pas les performances que l'on connaît maintenant et notamment la résistance de collecteur était importante d'où la nécessité d'utiliser des tensions importantes . Il réalise un schéma à l'aide de composants discrets qu'il fait breveter en 1956. Les images ci dessous sont empruntées au site:

L'oscillogramme met en évidence les performances

du circuit, le signal inférieur met en évidence le signal de

sortie de la porte. L'échelle est 20 mμs par carreau soit 20 ns par

carreau , la période du signal est 100ns c'est à dire une fréquence

de 10 MHz et si nous appliquons les critères actuels qui définissent les

temps de montée et descente d'un signal : temps pour passer de Vmini+10%

à Vmaxi-10%, les temps de montée sont proches de 5 à 10

nanosecondes .

1962 - Jan Narud:

a obtenu son doctorat de génie électrique et de

physique en 1954 à l'université de Stanford. Il a ensuite enseigné à

Harvard. Après une période de 5 années dans les laboratoires d'IBM

, il entre en 1961 chez Motorola en tant que directeur d'un

service de recherche . Il va être à l'origine de la famille de

circuits intégrés MECL10 000 ou MECL10K (Multi Emetteur Coupled

Logic) . Dés 1962 sort la première famille de circuits

ECL , puis MECL 2 en 1966, MECL 3 ou 1600 en

1968, MECL 10K en 1971.

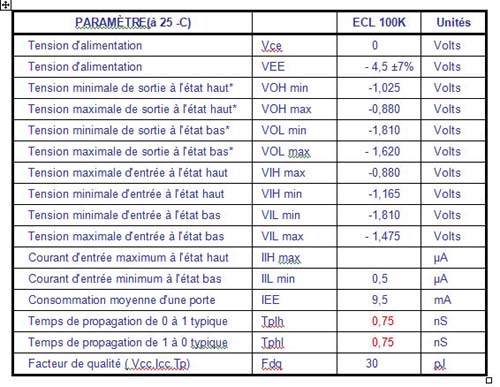

Dans le tableau ci dessus on voit que la

différence entre VOH et VOL va être compris entre 0,9V (VOHmax -

VOLmin) et 0,6 V (VOHmin - VOLmax), l'excusion de la tension de

sortie est faible, il en découle une faible immunité aux bruits. |

||||

|

Les étapes jusqu'aux CCD

|

|