|

|

|||||

|

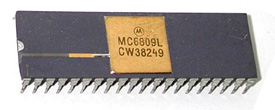

1971 - Le microprocesseur Motorola 6800 Microprocesseur 8 bits rťalisť ŗ l'aide transistors MOS ŗ dťplťtion canal N Le boÓtier DIP 40 broches, alimentť en 5V consomme de 0,5 ŗ 1 W Le chip est muni de deux bus, le bus de donnťes de 8 bits bidirectionnel, le bus d'adresses de 16 bits Il possŤde un jeu de 72 instructions, Horloge externe de 1 ŗ 2 MHz Caractťristiques d'implantation: 7000 transistors, gravure 6 μm, surface de silicium 16,5 mm2 Le choix de MOS ŗ dťplťtion a ťtť imposť par la nťcessitť de rťduire la taille la puce de silicium. A l'ťpoque les tranches de silicium permettant l'implantation des circuits ťtaient de 3 pouces (76mm) , sur un tel wafer on peut obtenir 190 circuits de 4,6mm de cotť ou 140 de 5,4mm , d'autre part plus le circuit est grand plus la probabilitť de la prťsence d'une impuretť dans ce circuit est grande, le rendement est de l'ordre de 20 ŗ 28% , c'est ce qui a guidť le choix technologique de MOS ŗ dťplťtion qui a permis de rťduire la taille du circuit ŗ 4mm Suite fiche : Texas SBP 0400 techno I2L |

|

||||

|

1976 - Le microprocesseur Motorola 6802 C'est un 6800 amťliorť incluant une horloge interne et 128 octets de RAM Suite des fiches "informatique" Zilog Z80 |

|

||||

|

|

|

||||

|

|

|

||||

|

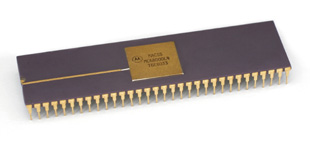

1984

- Le microprocesseur

Motorola 68020

Microprocesseur 32 bits rťalisť ŗ l'aide de 200 000 transistors en technologie HCMOS Boitier PGA 169 broches (114 broches employťes) Alimentť en 5V il consomme 1,75 W Cadencť par une horloge interne ŗ la frťquence de 12 MHz ŗ 33 MHz (5 MIPS ŗ 33 MHz) suivant les modŤles. Il possŤde un jeu de 101 instructions dont la multiplication de 2 nombres de 32 bits rťsultat sur 64 bits et la division d'un nombres de 64 bits par un de 32 bits rťsultat sur 32 bits pour le quotient et 32 bits pour le reste. Les bus de donnťes et d'adresses de 32 bits, Alimentť en 5V il consomme de 1,5 ŗ 1,7 W Cadencť par une horloge interne ŗ la frťquence de 8 MHz ŗ 16 MHz suivant les modŤles. Caractťristiques d'implantation: Gravure 2 μm surface de silicium 82 mm2 Suite des fiches "informatique": Le Macintosh d'Apple |

|

||||

|

1987

- Le microprocesseur

Motorola 68030

Microprocesseur 32 bits rťalisť ŗ l'aide de 273 000 transistors technologie CMOS et HMOS (High density MOS) Boitier PGA 128 broches ou en QFP 132 pins Alimentť en 5V il consomme 2,6 W Cadencť par une horloge interne ŗ la frťquence de 16 MHz ŗ 50 MHz (18 MIPS ŗ 50MHz) suivant les modŤles. Il inclut la MMU, unitť de management de la mťmoire qui permet notamment de paginer la mťmoire et d'en accroÓtre la rapiditť d'accŤs Caractťristiques d'implantation: Gravure 3μm surface de silicium ? mm2 Suite des fiches "informatique": Le 80386 d'Intel |

|

||||

|

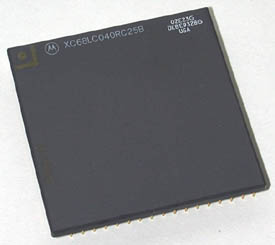

1989

- Le microprocesseur

Motorola 68040

Microprocesseur 32 bits rťalisť ŗ l'aide de 1 200 000 transistors CMOS Boitier PGA 179 broches ou en QFP 184 pins Alimentť en 5V il consomme 2,6 W Cadencť par une horloge interne ŗ la frťquence de 25 MHz ŗ 40 MHz suivant les modŤles. Il inclut la MMU, unitť de management de la mťmoire qui permet notamment de paginer la mťmoire et d'en accroitre la rapiditť d'accŤs ainsi que l'unitť de calcule en virgule flottante FPU Caractťristiques d'implantation: Gravure 0,8μm puis 0,65 Alimentť en 5V il consomme 2,6 W pour la premiŤre fois les performances du microprocesseur Motorola du moment sont infťrieures ŗ celles du microprocesseur INTEL 80486 ( |

|

||||

|

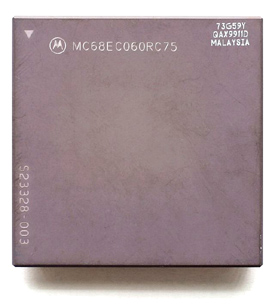

1994

- Le microprocesseur

Motorola 68060

Microprocesseur 32 bits rťalisť ŗ l'aide de 2 500 000 transistors CMOS Boitier PGA 206 broches ou en QFP 184 pins Alimentť en 5Vpour les entrťes/sorties et 3,3V pour le cúur il consomme 2,6 W Cadencť par une horloge interne ŗ la frťquence de 50 MHz ŗ 75 MHz suivant les modŤles.(88 MIPS ŗ 66MHz, 110 MIPS ŗ 75MHz et 36 MFlops ŗ 66MHz) Il inclut la MMU, unitť de management de la mťmoire qui permet notamment de paginer la mťmoire et d'en accroitre la rapiditť d'accŤs ainsi que l'unitť de calcule en virgule flottante FPU Caractťristiques d'implantation: Gravure 0,6 μm puis 0,42 μm |

|

||||

|

1994

- Le microprocesseur

AIM PowerPC 601 Ce microprocesseur est nť de la collaboration entre 3 sociťtťs Apple, IBM, Motorola (AIM) Microprocesseur 32 bits rťalisť ŗ l'aide de 2 800 000 transistors CMOS Boitier PGA 206 broches ou en QFP 184 pins Alimentť en 3,3V il consomme 6,5W ŗ 50MHz W Le bus de donnťes est de 64 bits et le bus d'adresses 32 bits Cadencť par une horloge interne ŗ la frťquence de 50 MHz ŗ 80 MHz Architecture RISC Caractťristiques d'implantation: Gravure 0,6 μm puis 0,42 μm sur 121mm2 de sicilicium Une seconde version sortie quelques mois plus tard avec une gravure de 0,5 μm se contera de 74 mm2 de silicium et est cadencť par une horloge ŗ 100, 110 ou 120 MHz |

|

||||