Les

mémoires RAM Statiques

Les premičres RAM

statiques ont été crées en 1968, elles sont présentées simultanément

chez Intel et chez Fairchild . Elles ont toutes deux une capacité de

1Kbits.

La mémoire RAM de Fairchild , la 93415 est réalisée en

transistors bipolaires , celle d'Intel la 2115 est en technologie

MOS

La premičre RAM

Motorola (6810) qui accompagnait la sortie du microprocesseur 6800

en 1972 avait une capacité de 128 octets (1Kbits également)

Les mémoires RAM, Mémoire ŕ

lecture aléatoire, ici aléatoire n'a pas le sens habituel , il

signifie que l'on peut lire un bit ou un octet quelconque en

précisant son adresse.

Ceci s'oppose aux mémoires ŕ lecture

séquentielle, essentiellement composées de registres ŕ décalage qui

demandent de faire défiler les mots stockés jusqu'ŕ ce que le mot

recherché se présente sur la sortie. Si la mémoire n'est pas

rebouclée sur elle męme, les information contenues se perdent ŕ la

sortie des registres.

Exemple: mémoire FIFO (first in, first out - premier entré , premier

sorti) genre file d'attente (ou buffer) pour une imprimante la

vitesse de fourniture des octets ŕ imprimer est plus grande que la

vitesse d'utilisation de l'imprimante. L'ordinateur rempli ŕ sa

vitesse 8 registres en parallčle , l'horloge est alors fournie par

l'ordinateur, lorsqu'il sont pleins l'imprimante demande octet par

octet ŕ son rythme l'horloge est fournie par l'imprimante. Le

premier octet fourni par l'ordinateur sera le premier ŕ sortir

d'oů le terme de FIFO.

Principe des mémoires RAM

Les mémoires RAM sont destinées au stockage temporaire des

données. En l'absence d'alimentation électrique la mémoire s'efface

. A l'origine, une mémoire se composait de cellules élémentaires

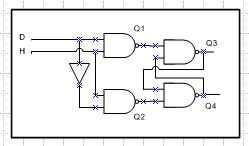

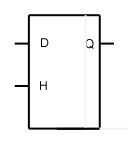

telle des bascules D représentées ci dessous

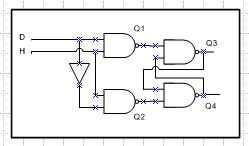

Cellule élémentaire: Lorsque l'horloge H est en position

basse H=0 les deux sorties Q1 et Q2 sont en position haute, Q1=Q2=1.

Les deux portes de sortie restent dans la position antérieure.

Si H=1 et D=0 la sortie Q2 =0 et Q1=1 → Q4=1 et Q3=0

Si H=1 et D=1 la sortie Q1 =0 et Q2=1 → Q3=1 et Q4=0

on voit que la sortie Q3 recopie

l'entrée D et Q4 est toujours le complément de Q3.

Table

de vérité de la

porte Nand

|

I1 |

I2 |

S |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

|

Schéma de base du latch(*) D

|

Table de vérité du bistable D

Π=

passage de 0 ŕ 1 puis ŕ 0 |

Symbole

|

(*) Une bascule ne peut changer d'état qu'une fois par cycle d'horloge sur front ou sur niveau, un latch

(ou verrou) est transparent lorsque l'horloge est en position

haute et verrouille l'information lorsque l'horloge retombe ŕ

l'état bas.

Cellule mémoire

La cellule mémoire doit pouvoir ętre adressée c'est ŕ dire que l'on

doit pouvoir désigner une cellule parmi les milliers intégrées sur

le circuit. La cellule doit pouvoir ętre le sičge d'une écriture,

stockage d'un bit en mémoire ou d'une lecture du bit stocké dans la

mémoire. Toutes ces opérations doivent pouvoir ętre synchronisées

par un signal d'horloge.

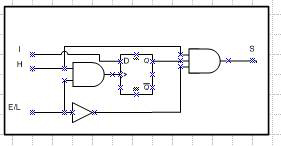

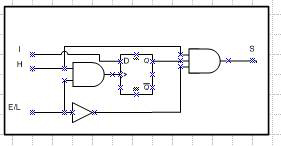

Dans le schéma ci dessous l'entrée E/L va orienter le pulse mémoire

soit pour une écriture E/L = 1 , la porte ET d'entrée est validée le

bit présent en I va ętre stocké dans le bistable sous l'effet de

l'impulsion d'horloge. Si E/L = 0 la

porte ET d'entrée est bloquée ŕ 0 le bistable est alors insensible ŕ

l'état de I, par contre la porte de sortie est validée et l'état

de la sortie Q est envoyé sur la sortie synchronisé par l'horloge.

La cellule élémentaire et son symbole

L |

|

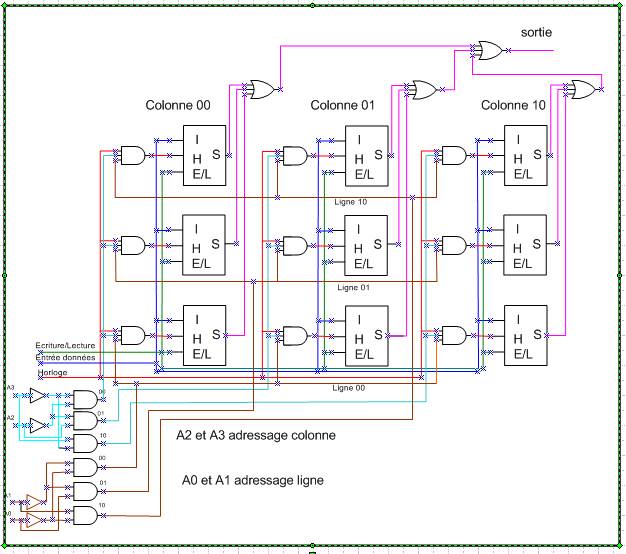

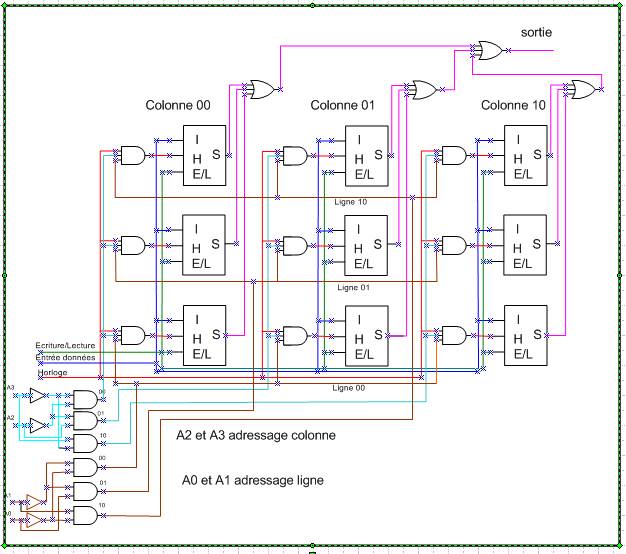

Dans le schéma ci dessous une

mémoire de 9 bits est réalisée ŕ titre d'exemple. Le circuit de

décodage d'adresse va orienter le pulse d'horloge sur la bonne

cellule , l'entrée E/L va préciser si c'est une opération de lecture

ou d'écriture . Ainsi si tous les bits d'adresse sont ŕ 0, c'est la

cellule ligne 00 et colonne 00 qui sera sélectionnée

Pour stocker des octets on imagine 8

plans mémoire en parallčle, les 8 entrées de données et les 8

sorties seront distincts l'Horloge sera commune ainsi que les bits

d'adressage. Un seul circuit de décodage de l'adresse sera utilisé.

On pourra ajouter des entrées de sélection du composant ( chip

select = cs) qui permettront d'associer plusieurs circuits les

entrées cs servant ŕ l'adressage des circuits.

Evidemment un tel circuit est tributaire de l'alimentation

électrique, en cas de coupure d'alimentation, toutes le cellules se

retrouvent en un état indéterminé.

Les mémoires

RAM CMOS

Avec l'arrivée des circuits CMOS la cellule mémoire s'est

fortement simplifiée. On rappelle que ŕ l'origine des MOS, seuls les

MOS P pouvaient ętre fabriqués avec un rendement suffisamment élevé

pour que le prix de revient soit intéressant, ensuite, avec

l'amélioration de la technologie de fabrication des monocristaux les

MOS N, plus rapides que les P ont pu ętre réalisés. Ce n'est qu'

aprčs cette étape que la technologie des CMOS est arrivée, en effet

un MOS P doit ętre réalisé sur un substrat N et un MOS N sur un

substrat P implanter les deux P et N sur un męme substrat était

compliqué d'autant plus que le phénomčne parasite de Latch Up est

apparu obligeant d'éloigner les deux transistors l'un de l'autre ce

qui nuit ŕ la densité d'intégration. (explication

plus détaillée)

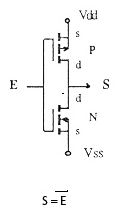

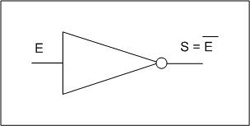

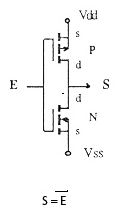

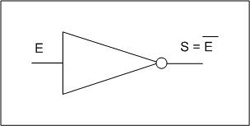

rappel sur l'inverseur CMOS:

|

Porte inverseuse CMOS |

Symbole |

|

|

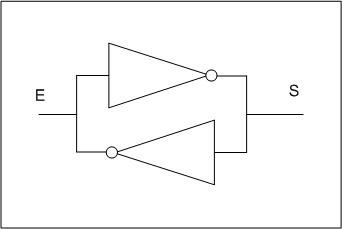

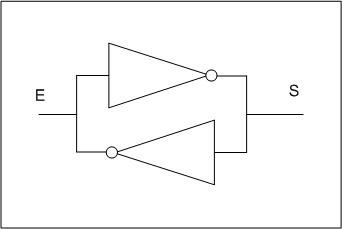

Cellule RAM statique CMOS

La cellule RAM CMOS est composée de deux inverseurs CMOS tęte bęche

Si nous appliquons sur

l'entrée E un 0 logique ,(signal extérieur), la sortie S

de la porte supérieure passe ŕ 1 et la porte inférieure

fournit ŕ son tour du 0 sur E, l'ensemble des cellules

va se maintenir dans cet état męme si nous supprimons le

signal extérieur . Ceci ne peut raisonnablement se faire

que si la résistance de sortie des portes est grande car

si on force l'entrée, qui était précédemment ŕ 1, ŕ 0 cela revient ŕ

court-circuiter la sortie de la porte inférieure.

Ces

portes n'ayant pour fonction que la conservation d'un

état logique, elles n'ont pas ŕ fournir de courant, les

résistances de canal peuvent donc ętre trčs importante

sans inconvénient.

La cellule RAM statique CMOS ne nécessitera que 4

transistors et consomme trčs peu. |

|

Les mémoires

RAM

Dynamiques

L'organisation des mémoires dynamiques est identique la

précédente mais la cellule élémentaire est réduite ŕ sa plus simple

expression, le bit est stocké dans la capacité de grille d'un

transistor. Cette capacité étant trčs faible l'information ne peut

se conserver trčs longtemps , il faut rafraichir la mémoire (refresh)

une entrée refresh doit recevoir un signal dont la périodicité est

fixée par le constructeur, la mémoire n'est pas utilisable durant le cycle de "refresh" . Pendant

ce cycle des éléments internes estiment l'état de chaque capacité.

Au dessus d'un certain seuil la capacité est rechargée, en dessous

la capacité est vidée .

A un moment donné de la technologie des circuits intégrés les

mémoires RAM dynamiques dont la cellule de base nécessite moins de

transistors que la statique ŕ une capacité supérieure

En 1970, Intel sort sa premičre mémoire DRAM de 1kbits chaque

cellule est réalisé ŕ l'aide de 3 transistors ( il en faut 6 pour

une RAM) le circuit est réalisé ŕ l'aide de 5000 transistors MOS P

grille au silicium

En 1974 c'est une DRAM de 4kbits dont la cellule élémentaire est

composée d'un seul transistor MOS N grille au silicium.

Les mémoires RAM ou DRAM et tous les

autres circuits intégrés seront tributaires des techniques de

gravure ainsi les progrčs ont été fulgurants le tableau ci dessous

en fait foi

| |

1971 |

1981 |

1989 |

1998 |

2007 |

| Gravure en μm |

10 |

3 |

0,8 |

0,25 |

0,09 |

| Capacité des DRAM |

1K |

64K |

4M |

256M |

16G |

Les étapes jusqu'aux CCD